Про ASIC-и, FPGA-сики и ProASIC-и... ч.1

Поскольку альтернативного, экономически-целесообразного и энергетически-эффективного решения для высокопроизводительных вычислений, акромя использования микросхем программируемой логики (ПЛИС) или заказных СБИС (ASIC), в настоящее время не просматривается, то надо к ним повнимательнее приглядеться ... Информации по теме ПЛИС достаточно много на просторах интернета и в печатном виде, но она разбросана либо по отдельным производителям, либо освещает лишь некоторые аспекты. Решил создать здесь широкий обзор тематики, так как на мой взгляд, у многих интересующихся прикладным применением устройств для майнинга, наблюдается недостаток информированности об этих устройствах и используемых в них технологиях. Многие очевидно считают, что технология ASIC это более совершенный вариант реализации FPGA-технологии. Ничего подобного ! Обывательские разговорчики. (с). Итак, попробуем поковыряться у них в кишках и разобраться что к чему.

Поскольку альтернативного, экономически-целесообразного и энергетически-эффективного решения для высокопроизводительных вычислений, акромя использования микросхем программируемой логики (ПЛИС) или заказных СБИС (ASIC), в настоящее время не просматривается, то надо к ним повнимательнее приглядеться ... Информации по теме ПЛИС достаточно много на просторах интернета и в печатном виде, но она разбросана либо по отдельным производителям, либо освещает лишь некоторые аспекты. Решил создать здесь широкий обзор тематики, так как на мой взгляд, у многих интересующихся прикладным применением устройств для майнинга, наблюдается недостаток информированности об этих устройствах и используемых в них технологиях. Многие очевидно считают, что технология ASIC это более совершенный вариант реализации FPGA-технологии. Ничего подобного ! Обывательские разговорчики. (с). Итак, попробуем поковыряться у них в кишках и разобраться что к чему.

Программируемые логические интегральные схемы (ПЛИС) – один из продуктов прогресса микроэлектронной промышленности, применяемый для реализации всевозможных цифровых устройств самой разной сложности. Появились они около 20-ти лет назад и быстро завоевали лидерство в области разработки схемных решений для цифровых устройств. Основные производители ПЛИС: корпорации "Altera", "Xilinx", "Lattice semiconductor", "Actel".

Диапазон применения ПЛИС очень широк: от простых счетчиков и преобразователей кодов, несложных цифровых схем, ранее реализуемых на рассыпухе до специализированных вычислителей или различных процессоров, вплоть до создания нейронной сети.

Таким образом, некоторое цифровое устройство, которое было разработано лет 15-20 назад, располагалось на десятке плат и занимало целую корзину в монтажной стойке, теперь может быть реализовано на одной небольшой печатной плате. Мало того: при использовании ПЛИС появляется возможность без особых усилий и затрат изменить функциональную наполненность всего цифрового устройства - путем изменения конфигурации ПЛИС. Чего раньше (при использовании дискретных логических микросхем (рассыпуха)) невозможно было сделать без доработки и изменения устройства. Зачастую проще было разработать новое устройство, чем дорабатывать и доводить до ума старое.

Как пример реализации оборудования с заменой устаревшей элементной базы на относительно дешевую и небольшую ПЛИС + небольшой микроконтроллер, приложу видео с моим прожектом модернизации итальянского упаковочного автомата 30-летнего возраста. Здесь вся электронная система управления, занимавшая небольшой шкафчик, уместилась в маленькую симпатичную коробочку. Некоторое врямя этот девайс успешно работал. Жаль только, что фабрика та сгорела к монахам вскоре после пробных испытаний устройства ... :huh:

http://www.youtube.com/watch?v=03GUqF1SasU&list=HL1362376730

Сегодня ПЛИС делятся на две основные группы: CPLD(Complex Programmable Logic Device) и FPGA(Field-Programmable Gate Array).

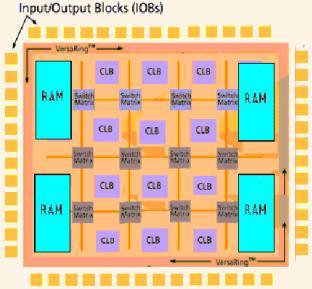

В буквальном переводе, первая группа - это Сложные Программируемые Логические Устройства, а вторая - Программируемая Пользователем Вентильная Матрица. CPLD как и FPGA структурно состоят из матрицы логических блоков, матрицы соединений, блоков ввода-вывода и конфигурационной памяти, хранящей топологию связей между логическими блоками.

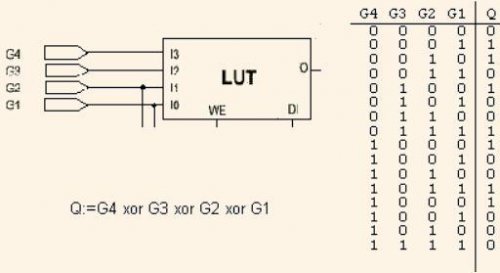

Принципиальная разница между ними в том, что у CPLD базовый слой содержит укрупненные логические блоки на основе элементарных вентилей (2И-НЕ/2ИЛИ-НЕ), а у FPGA этот слой содержит более компактные логические ячейки на основе таблиц истинности (LUT) и количество логических ячеек в базовом слое FPGA превышает количество онных в CPLD на 1-2 порядка. Вследствие этого FPGA имеет более гибкую архитектуру.

Также необходимо добавить, что FPGA в отличие от CPLD, могут содержать на базовом слое специальные ядра, ускоряющие специфические алгоритмы обработки (DSP-блоки), а также блоки памяти. Процесс программирования ПЛИС заключается в переносе конфигурации матрицы соединений на специальную внутреннюю память ПЛИС. В этом аспекте CPLD и FPGA (почти все) заметно отличаются. Если CPLD содержит прямо на кристалле энергонезависимую конфигурационную память, но с ограниченным количеством циклов программирования, то почти все представители семейства FPGA содержат на кристалле блок энергозависимого ОЗУ в качестве конфигурационной памяти. Данную память при старте системы нужно загрузить конфигурационной информацией, которая обычно располагается во внешнем ППЗУ (параллельного или последовательного типов).

Данная технология загрузки конфигурации с внешней памяти практически не имеет ограничения на количество циклов программирования, т.к. современные Flash-ППЗУ допускают до 100 000 циклов перезаписи. Но данная технология имеет один серьезный недостаток: она требует некоторого времени для загрузки конфигурации и при этом процессе происходит заметный бросок потребляемого системой тока, что создает дополнительные требования к цепям питания и фильтрации. Если читатели помнят, то я написал, что такую технологию конфигурирования (SRAM-технологию) поддерживают почти все FPGA. Но... не все. Если FPGA-чипы основных мировых производителей "Altera" и "Xilinx" построены на данной технологии, то FPGA-чипы менее именитого производителя - корпорации "Actel", построены по FLASH-технологии конфигурационной памяти. Это значит, что свою конфигурацию эти FPGA сохраняют и при выключенном питании, а при включении - данный тип FPGA мгновенно готов к работе. Кроме того, данная технология конфигурирования FPGA не только избавлена от начальных бросков тока при загрузке, но и сокращает энергопотребление кристалла, а также в несколько раз уменьшает размеры конфигурационной ячейки, что позволяет более эффективно использовать площадь кристалла. Вообще говоря, FPGA от "Actel" мне представляются наиболее интересными для использования под майнинг ввиду привлекательных цен и хорошей энергоэффективности. На них я остановлюсь подробнее чуть ниже.

Корпорация "Lattice semiconductor" избрала третий (гибрридный) вариант реализации конфигурирования FPGA: у них также как у "Altera" и "Xilinx" задействована SRAM-технология загружаемой конфигурирации, но FLASH-память конфигурации расположена не снаружи, а внутри кристалла.

Выпускаемые FPGA делятся по ценовому и функциональному критериям на несколько сегментов: нижний, средний и топовый. У корпорации "Altera" разные сегменты FPGA представлены такими семействами как Cyclone(нижний), Arria(средний) и Stratix(топовый). У корпорации "Xilinx" до недавного времени было два сегмента, которые были представлены семействами Spartan(нижний) и Virtex(топовый). На данный момент между ними расположились еще два: Artix и Kintex.

Продолжение следует...

11 Комментариев

Рекомендуемые комментарии

Для публикации сообщений создайте учётную запись или авторизуйтесь

Вы должны быть пользователем, чтобы оставить комментарий

Создать учетную запись

Зарегистрируйте новую учётную запись в нашем сообществе. Это очень просто!

Регистрация нового пользователяВойти

Уже есть аккаунт? Войти в систему.

Войти